Э. КЛИНГМАН

ПРОЕКТИРОВАНИЕ

МИКРОПРОЦЕССОРНЫХ

СИСТЕМ

Перевод с английского

канд. техн.

наук В. А. Балыбердина

и В. А. Зинченко

под редакцией

д-ра техн.

наук С. Д. Пашкеева

===============================

ИЗДАТЕЛЬСТВО «МИР»

Москва 1980

=======================================================

_____________________ Структуры прерываний стр. 445

Микропроцессор 9900 фирмы Texas Instruments

Микропроцессор

ТI9900 - первый

микропроцессор третьего поколения.

Его архитектура хорошо приспособлена для контекстного переключения, т.е. для

обработки прерываний. ТI9900 - микропроцессор

с командами типа память-память, т.е. без блока внутренних регистров. Все

команды обработки данных выбирают данные из памяти, выполняют над ними соответствующие операции в ЦП и пересылают

результат в ЗУ. Таким образом, нет необходимости сохранять и восстанавливать содержимое

регистров, как в других

микропроцессорах. Сохраняют и восстанавливают содержимое только трех рабочих регистров: СК, регистра

состояния и указателя

рабочей области. В некотором смысле это напоминает сохранение «метасостояния» в микропроцессоре СОSМАС фирмы RСА.

Указатель рабочей области выбирает первые 32 ячейки памяти, которые выполняют функции регистров

общего назначения или рабочей

области. Блок рабочих регистров используют в связи с тем, что пересылка типа регистр-регистр

гораздо быстрее пересылок

типа память-память. Так как время обращения к ЗУ с n-МОП-структурой менее 100 нс,

пересылки типа память-память выполняются так же быстро, как и пересылки в ЦП. При использовании микропроцессора в режиме с

большим числом контекстных переключений

такая архитектура более эффективна, так как исключает сохранение и восстановление содержимого

регистров. Микропроцессор 9900 выполняет контекстное переключение за три цикла записи и три цикла выборки данных.

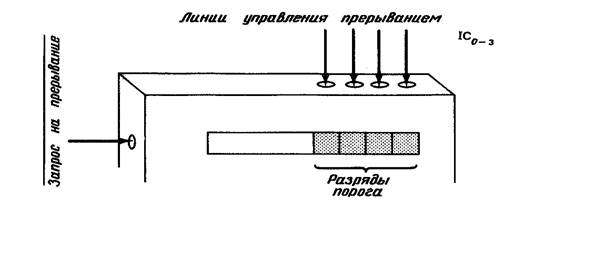

Структура прерываний микропроцессора

9900

Рис.12.31

Простой, но эффективной структуре прерываний микропроцессора 9900 присущи характерные

особенности как структуры прерываний микропроцессора РАСЕ, так и структуры прерываний микропроцессора Intel 8214 (рис. 12.31). Четыре разряда регистра состояния использованы под

код порога прерывания активного уровня. При поступлении запроса на прерывание

код, выдаваемый по четырем

линиям управления прерыванием (ICo—IC3), сравнивается с кодом порога

прерывания. Если первый

код больше или равен коду порога, происходит прерывание и устанавливается новый код

порога. В противном случае прерывание не имеет места. Для 16-уровневой системы

прерываний в памяти отведены ячейки 0—ЗС, из которых ЦП выбирает новое содержимое СК и указателя рабочей

области. Старый вектор

состояния (содержимое указателя рабочей области, СК и регистра состояния) сохраняется в регистрах

13, 14 и 15 новой 32-регистровой

рабочей области.

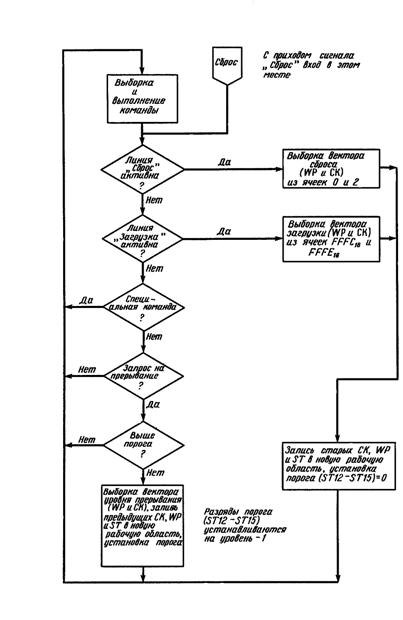

Сигналы «Сброс» и «Загрузка» (диаграмма

переходов на рис. 12.32) вызывают

обращение к

Рис.12.32

двум определенным ячейкам памяти. Две команды XOP и BLWP запрещают выдачу сигнала прерывания. После выполнения любой другой

команды проверяется поступление

запросов на прерывание. Если во время выполнения команды поступил запрос на

прерывание и если прерывание разрешено, содержимое разрядов управления прерыванием сравнивается с

маской порога прерывания в регистре состояния. Во время прерывания переключается контекст

и вычитается 1 из кода маски

состояния.